# Integrated Power Management with Switched-Capacitor DC-DC Converters

Hanh-Phuc Le, Michael Seeman, Vincent Ng., Mervin John Prof. Seth Sanders and Prof. Elad Alon

UC Berkeley, California

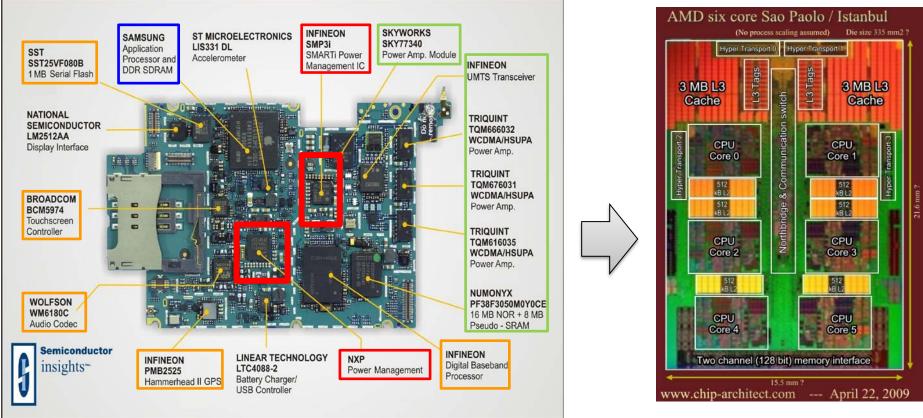

### **Integration Challenges**

- Integration has a benefit in energy efficiency

- Save IO power, board area

#### But it has a problem

Need different voltage supply for different blocks/IPs and different modes of operations (DVS).

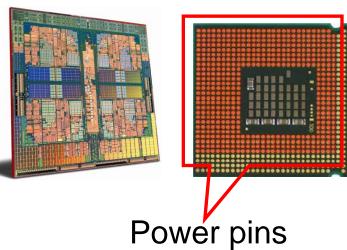

#### **Limited Resources**

- Functions on-die increases the need for separate supply

- But the resources (pins and decap) are limited

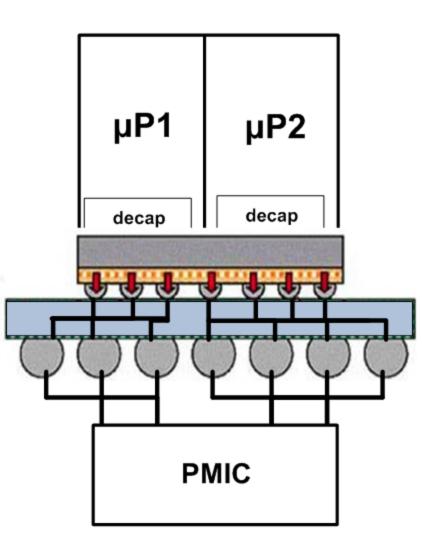

## Multiple Off-chip Supplies: Not Appealing

- Split power plane leads to supply impedance degradation

- Compensating by de-cap is areaconsuming → costly solution

- → Just supplying power from offchip is not appealing

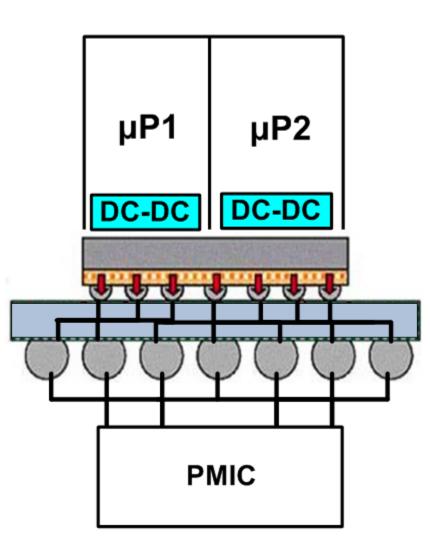

### **Integrated DC-DC Converters**

#### One global supply onto die

- Local power generated by fully integrated DC-DC converters

- Don't lose anything from package side

$\rightarrow$  How to make integrated DC-DC conversion efficiently?

### Outline

- Motivation

- Integrated converter efficiency

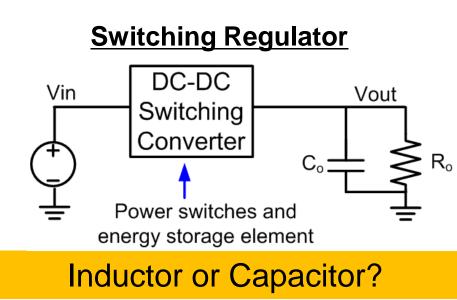

- Choice of energy storage element

- Efficiency analysis

- Switched-capacitor converter design and prototype

## DC-DC Converter: Linear vs. Switching

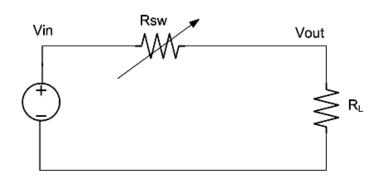

#### Linear Regulator

$$\eta = \frac{V_{out}}{V_{in}}$$

Fundamental limit on efficiency

- Efficiency is ideally independent of conversion ratio.

- Theoretically, can reach up to 100% efficiency

# $\bigcirc$

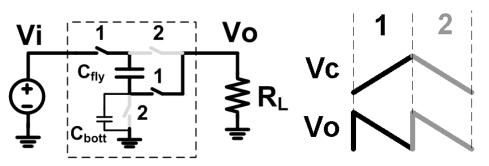

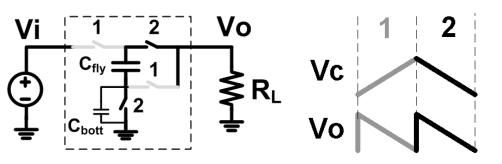

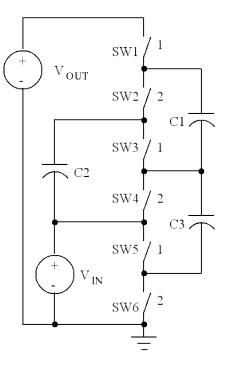

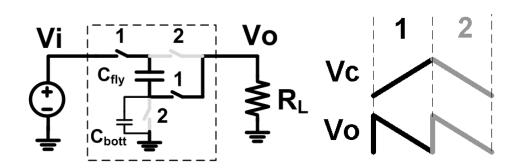

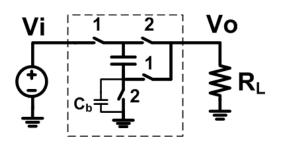

### SC – Operation of 2-to-1 Conversion

#### Phase 1

- Two-phase operation

- Phase 1: charge capacitor

#### Phase 2

Phase 2: capacitor transfers charge to output

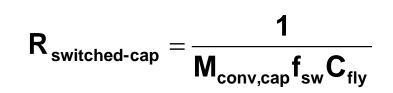

Equivalent resistance from loss over switched-cap

### **Switched Capacitor Power Converters**

- Only switches and capacitors

- Using no inductors has advantages:

- Simplified full integration potential

- Works well over a wide power range

- Single mode, can adjust clock rate

- No minimum load

- No inductive switching losses

#### • Open-loop loadline regulation possible:

Output impedance has R-C characteristic, with R naturally designed to meet efficiency spec

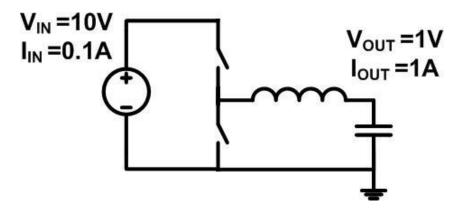

**First Look**

Magnetic boost/buck:

- 10-to-1 V conversion, 1A @ 1V

- S1,S2 rated for V-A product of

V\*I = 10 V-A

- Sum up to 20 V-A

- Need inductor, inductor loss,

- Inductive switching

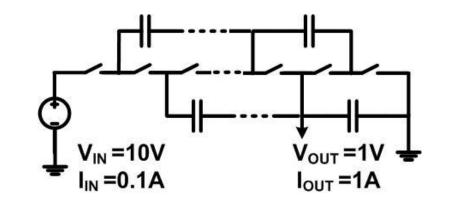

#### **10-to-1 Ladder Switched-Cap:**

- 10-to-1 V conversion, 1A@1V

- 20 switches, each blocks 1V

- 18 switches handle 1/5 A

- 2 switches handle 9/5 A

- V-A product sums up to 36/5 = 7.2 V-A

- Intrinsic CMOS device convenient

### **The Submicron Opportunity**

- Rate device by ratio:  $G_s V_s^2 / C V_g^2$

- Essentially an Ft type parameter for a power switch reflecting power gain

- Opportunity in scaling

- Suggests that we should look for opportunities to build our ckts with scaled CMOS based devices, but:

- Low voltage rating per device

- Inadequate metal/interconnect for high current?

### Why Not S-C?

- Difficult regulation?

- Not suited for high current/power?

- Magnetic-based ckts = higher performance?

- Interconnect difficulty for many caps?

- Voltage rating of CMOS processes?

- Ripple?

## **Previous Work**

| Work                              | [1]<br>Breussegem, VLSI 09 | [2]<br>Somasekhar, VLSI 09 |

|-----------------------------------|----------------------------|----------------------------|

| Technology                        | 130nm Bulk                 | 32nm Bulk                  |

| Тороlоду                          | 2/1 step-up                | 2/1 step-up                |

| Interleaved Phases                | 16                         | 32                         |

| Converter Area (mm <sup>2</sup> ) | 2.25                       | 6.678x10 <sup>-3</sup>     |

| Power density @ η <sub>max</sub>  | 2.09 mW/mm <sup>2</sup>    | 1.123 W/mm <sup>2</sup>    |

| Efficiency (η <sub>max</sub> )    | 82%                        | 60%                        |

| Die photo                         | EC FC FC C OUT             | Pump 0-15                  |

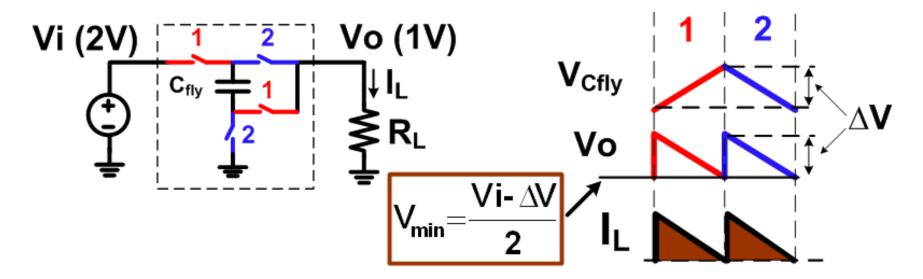

## **Switched Capacitor Loss**

- Converter supplies digital circuits

- Performance ( $f_{CPU}$ ) set by  $V_{min}$

- Intrinsic switched-capacitor loss:

$$\mathbf{P}_{\mathbf{C}_{fly}} = \underbrace{\mathbf{2x}}_{\mathbf{M}_{conv,cap}} \frac{\mathbf{I}_{L}^{2}}{\mathbf{M}_{conv,cap} \mathbf{f}_{sw} \mathbf{C}_{fly}}$$

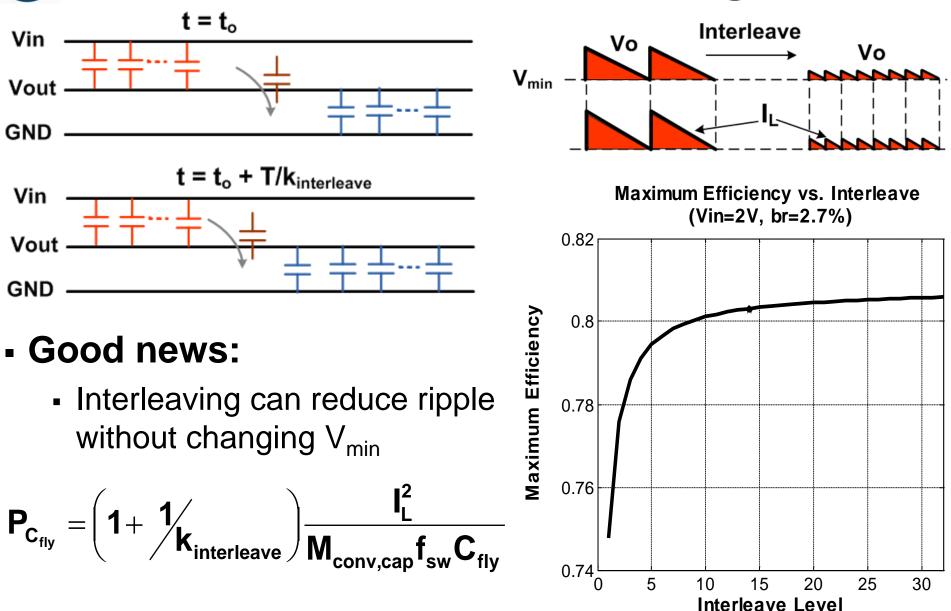

## **Multi-Phase Interleaving**

Ref: D. Ma, F. Luo, IEEE Trans. VLSI Sys., 2008

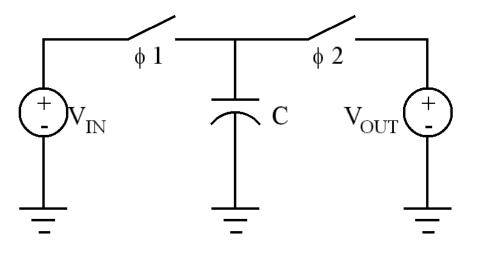

#### SC Analysis: Simplest Example

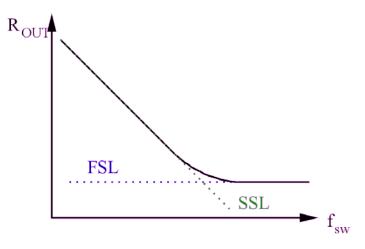

#### • Slow Switching Limit (SSL):

- Impulsive currents (charge transfers)

- Resistance negligible (assume R = 0)

- This (SSL) impedance is the switching loss!

- Fast Switching Limit (FSL):

- Constant current through switches

- Model capacitors as voltage sources  $(C \rightarrow \infty)$

$$i = f_{sw} \Delta q = f_{sw} C \Delta v$$

$$i = \frac{1}{4} \frac{1}{R} \Delta v$$

$$(\Delta v = V_{IN} - V_{OUT})$$

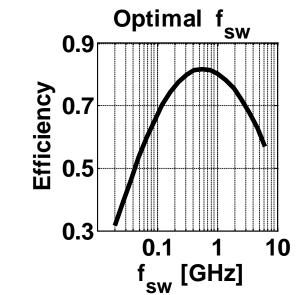

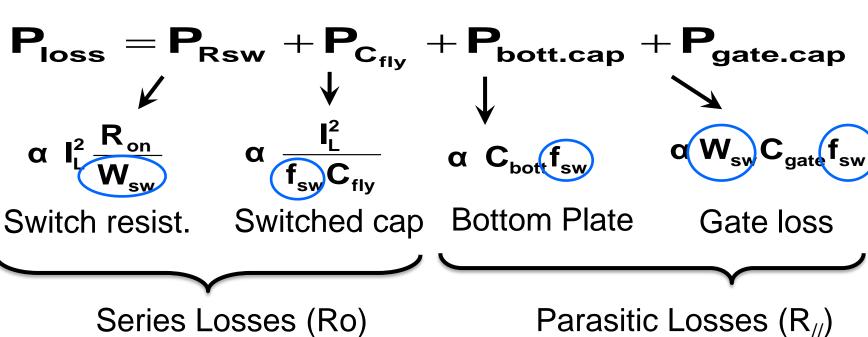

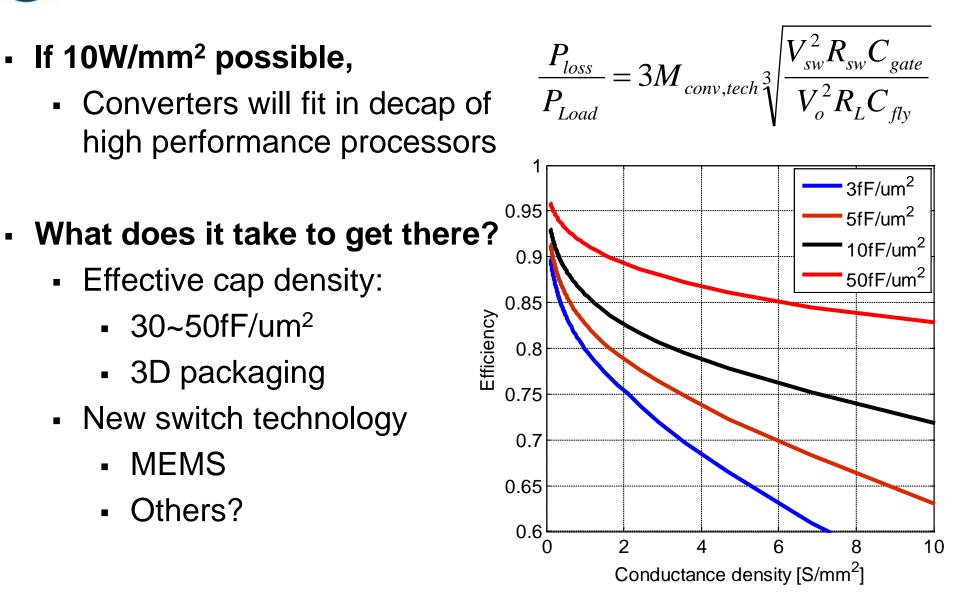

## **SC** – Loss Optimization

4 main loss components

### **Optimization for Efficiency**

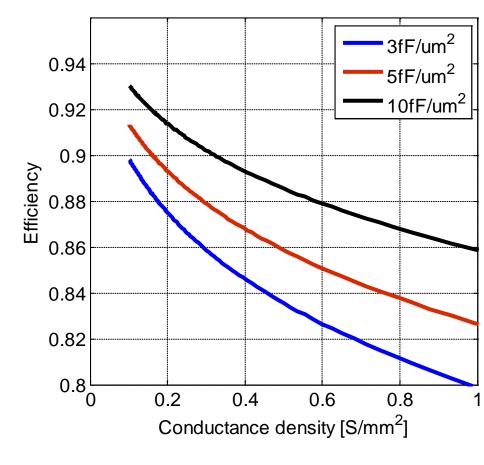

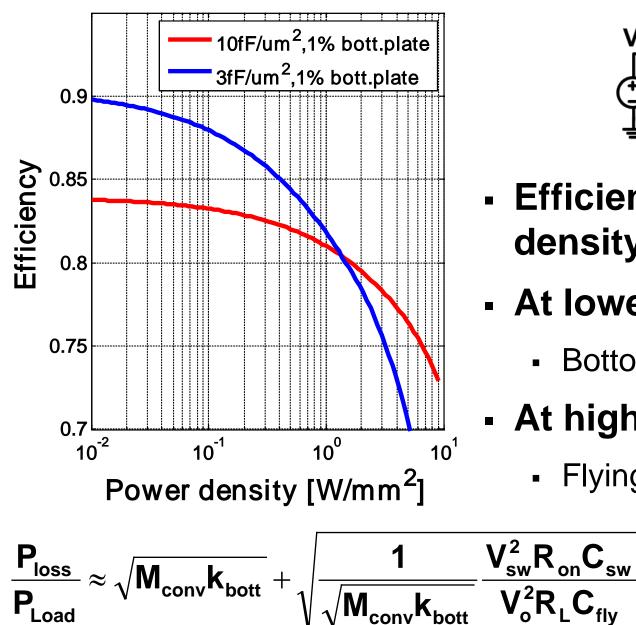

#### Efficiency vs. Cap. Density

$$\mathbf{P}_{\mathsf{loss}} = \mathbf{P}_{\mathsf{Rsw}} + \mathbf{P}_{\mathsf{C}_{\mathsf{fly}}} + \mathbf{P}_{\mathsf{bott.cap}} + \mathbf{P}_{\mathsf{gate.cap}}$$

No bottom plate cap, optimize switch sizes W<sub>sw</sub> and switching frequency f<sub>sw</sub>

$$\frac{P_{loss}}{P_{Load}} = 3M_{conv,tech} \sqrt[3]{\frac{V_{sw}^2 R_{sw} C_{gat}}{V_o^2 R_L C_{fly}}}$$

$\rightarrow$

## **Optimization for Efficiency**

- Efficiency and Power density trade-off

- At lower power density:

- Bottom plate critical

- At high power density:

- Flying cap critical

## **Achievable Performance**

#### Looks promising

- Especially in mobile applications

- 1W/mm<sup>2</sup> converter fits in decap area

- Only looked at 2:1 converter so far

- Need to support multiple output voltage levels

## Eff. vs. Cap Density

$(k_{bott} = 3\%)$

### Outline

- Motivation

- Integrated converter efficiency

- Choice of energy storage element

- Efficiency analysis

- Switched-capacitor converter design and prototype

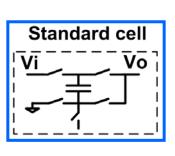

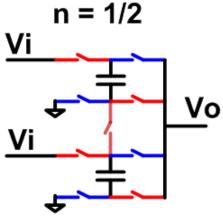

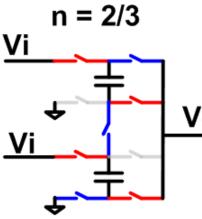

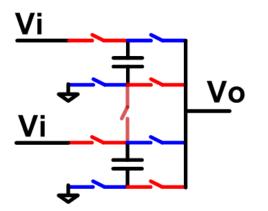

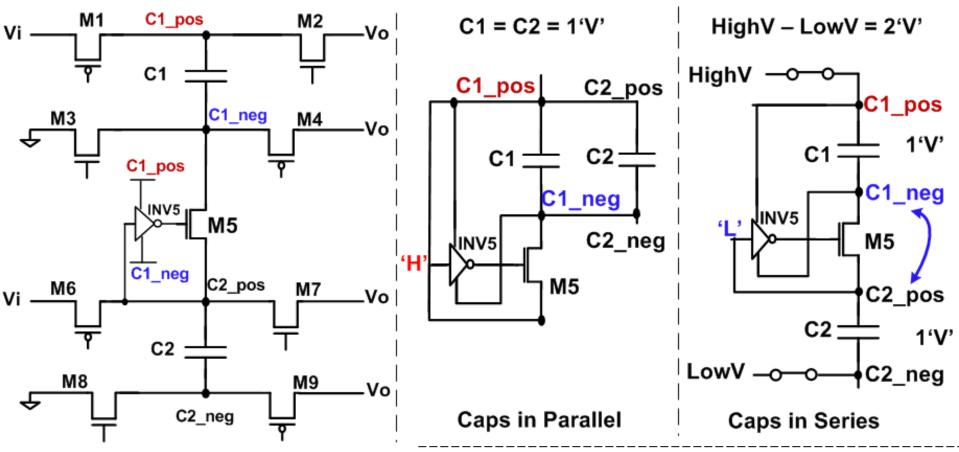

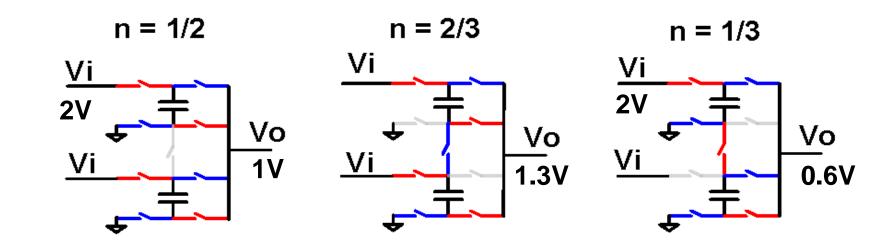

## **Multiple Conversion Ratios**

8

n = 1/3

- Standard cell design supports multiple conversion ratios

- Fine output voltages achieved by controlling f<sub>sw</sub> (or W<sub>sw</sub>)

- Equivalent to linearly regulating down from peak efficiency

- How to drive the switches?

<u>**Ref:</u>** D. Maksimovic and S. Dhar, *IEEE PESC, 1999*</u>

## **Switch Drivers**

- Most switches easy to drive

- 2 voltage domains:

- (Vi Vo)

- (Vo GND)

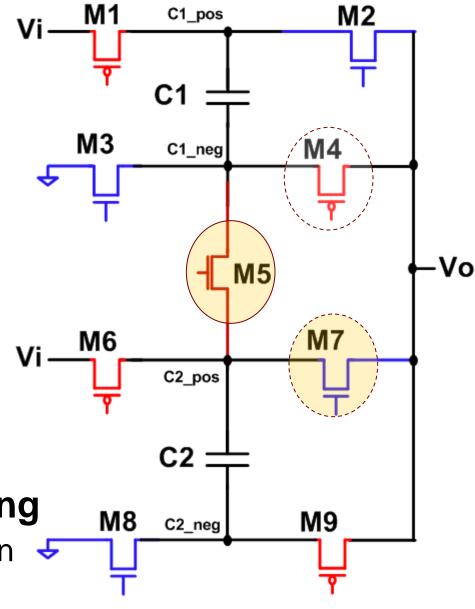

### M4, M5, and M7 challenging

Experience voltages between the two domains

Switch Driver – M5

- "Flying" inverter INV5 powered off of C1

- Controlled by top-plate of C2

Automatically synchronized by operation of other switches

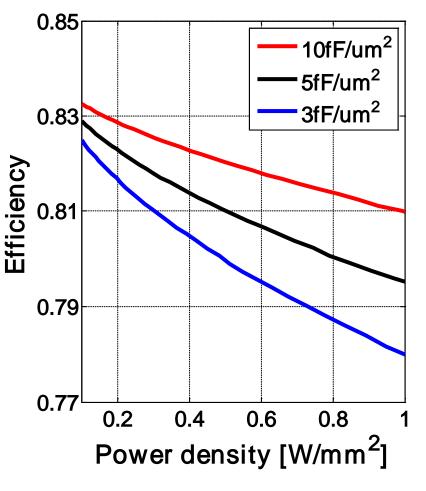

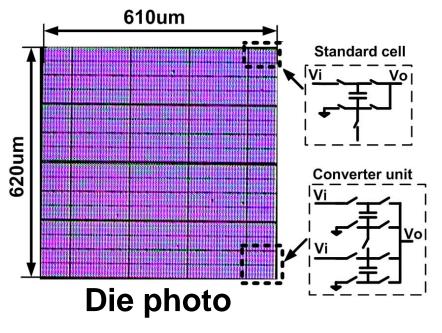

## **SC Converter Prototype**

Implemented in 32nm SOI test-chip

32-way interleaved

Supports 0.6V ~ 1.2V from 2V input

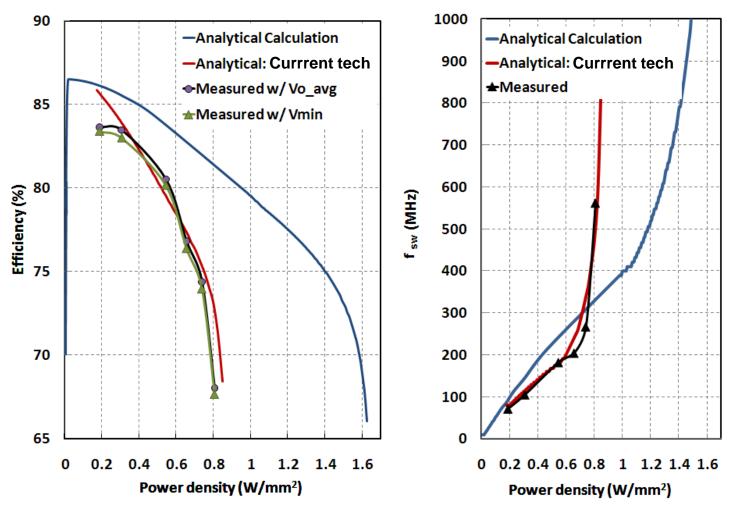

### Measured Eff. vs. P-density

- Measured in 1/2 mode (Vi = 2V, Vo ≈ 0.88V)

- Results promising: 81% efficiency @ 0.55 W/mm<sup>2</sup>

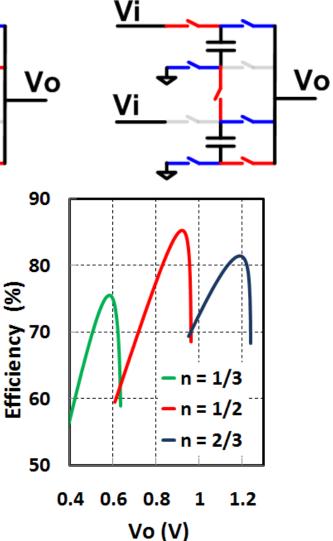

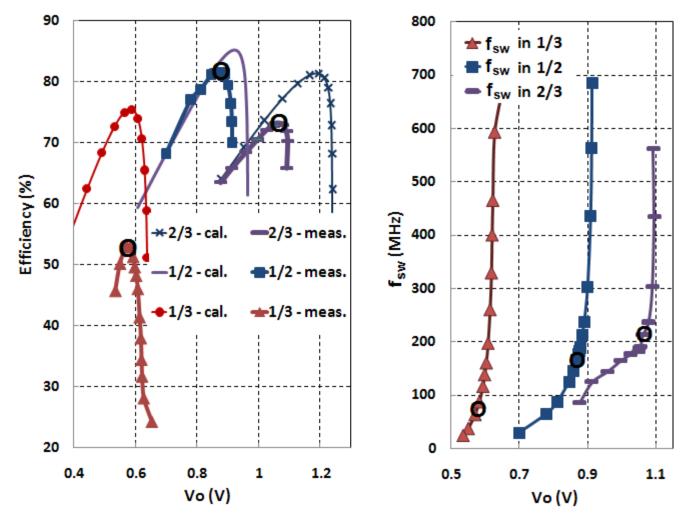

#### Measured Eff. vs. Topologies

Settings: Vi = 2V  $R_L \approx 4\Omega$  at Vo = 0.8V.

$f_{sw}$  vs. Vo

### How to get 10W/mm<sup>2</sup>?

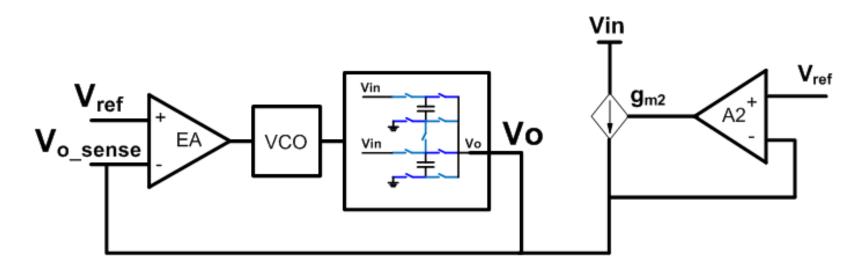

### **Hybrid Regulator**

#### Separate control range

- Switched-cap converter controls low frequency (DC) impedance

- Linear regulator controls high frequency (AC) impedance

- Only active when needed.

Ref: E. Alon and M. Horowitz, "Integrated Regulation for Energy-Efficient Digital Circuits," *IEEE J. Solid State Circuits*, vol. 43, no. 8, pp. 1795-1807, Aug. 2008.

## Conclusions

- Clear needs for fully-integrated DC-DC converters

- Switched—cap: a promising option

- First demonstration achieves both high power density and high efficiency

- In 2:1: 81% efficiency at 0.55W/mm<sup>2</sup>

- Reconfigurable to maintain efficiency over wide output voltage range

- >70% efficiency for Vo from ~0.7V to 1.15V

- Will need close-loop regulation and higher power density.

## Acknowledgement

#### - AMD

- Layout team in India (Siddika Gundlur, Uttam Singhal)

- Test team in Austin (Mike Bourland, Mike Jackson, Kevin Nguyen)

- NSF Infrastructure Grant No. 0403427

- IFC

- BWRC Sponsors

- C2S2